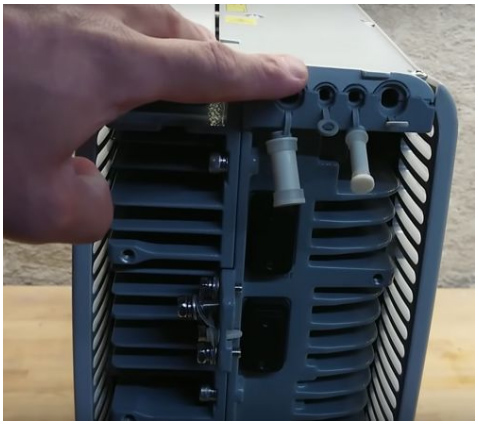

相信沒有人不認識華為的,那么華為作為全球第一大通信設備商,你知道華為的基站是怎么設計出來的嗎?它都用了哪些芯片?PCB電路設計結構如何?帶著一堆問題,我們拆解了華為RRU3908,一個戶外無線基站,它的每個射頻前端輸出功率為20/40瓦。

該基站的雙工器似乎是虹膜耦合腔濾波器,與一些腔間耦合。輸入和輸出的耦合是T,是諧振器上的一個連接部分,而不是耦合回路。頻率由電容帽調節。濾波器是寬信號的帶通。

如果能看到該過濾器的響應速度,那就更好了。

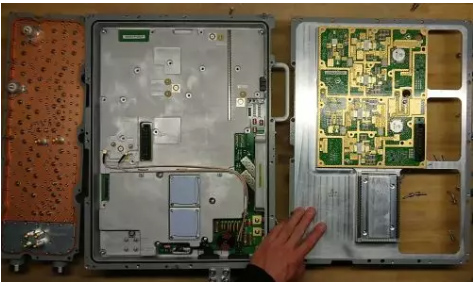

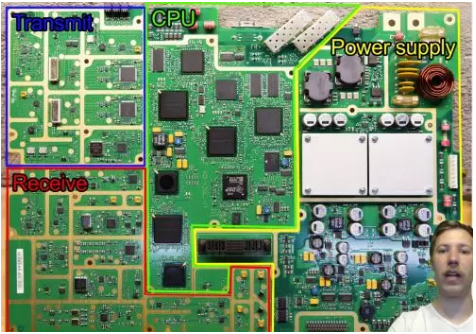

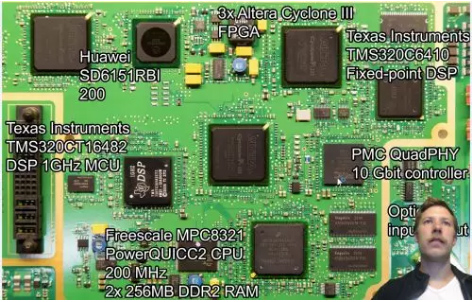

中央處理單元

網絡通信由飛思卡爾MPC8321 PowerQUICC2 CPU處理,CPU運行在200 MHz,擁有2x 256 MB Hynix DDR2 RAM。它使用一個PMC QuadPHY 10gb控制器用于兩個光學輸入/輸出。

ADC和DAC單比特流的解碼和編碼由3 Altera Cyclone III FPGA和定制的華為SD6151RBI控制器處理。

該華為基站采用德州儀器TMS320系列DSP處理器對單比特流進行處理。TMS320C6410是一個只計算整數的定點DSP, TMS320CT16482 1 GHz DSP CPU計算浮點數。

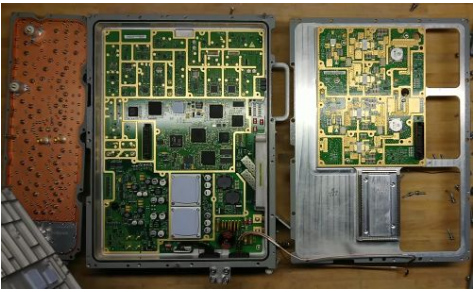

信號接收部分

輸入信號來自兩條失相線,首先由Skyworks SKY73021-11 1.7 - 2.2 GHz下變頻混頻器處理,得到2.2 GHz到550 MHz的頻率。

下變頻混頻器的本振為模擬器件ADF4110B。

一個SIPAT鋸過濾器用于隔離。

根據信號來源或類型的不同,假設在信號線分成3G ADC線或4G ADC線之前使用的是模擬設備AD8376可變增益放大器。

3G線路模擬到數字轉換由模擬設備AD6655-10處理,這是一個14位150 MSPS芯片,專門針對3G基站。

4G線有一些組件如有雙向HSWA + 1110領域射頻開關,為雙通道MAX2039E / dowoconversion混合器和通過一個額外的恢復期HSWA + 1110領域射頻開關是由模擬裝置ad9230 - 11 - 200 ADC芯片數200個。

所有的定時都是由模擬設備AD9516-3處理,這是一個14輸出時鐘發生器與內置在2 GHz本地振蕩器。

信號傳輸部分

Altera Cyclone III FPGA的單比特數據流由2個模擬設備TxDAC AD9788處理,TxDAC AD9788指定用于16位800 MSPS。

為了使信號的頻率上升到廣播載波頻率,使用了2個模擬裝置ADL5375-05上變頻調制器。它們的范圍從400mhz到6ghz。

然后信號通過5級陶瓷諧振器帶通濾波器發送。

信號相位可以從晶體管和EMC技術的設置和佛羅里達RF實驗室HPJ2F混合耦合器切換。

信號發送到功放前的前置放大器為飛思卡爾MMG3004NT1高線性放大器,可在400mhz ~ 2.2 GHz范圍內放大17 dB。

為了控制信號強度,MCL 31R5數字步進衰減器位于輸出連接器前。這是一個31.5 dB衰減器,可以在0.5 dB的步驟從一個6位串行控制接口。

功率放大器

功率放大器采用兩個階段,第一個階段是英飛凌PTMA180402FL 40瓦射頻LDMOS,通過Xinger II XC1900A-03S混合耦合器,將兩個90度非相位信號饋送給輸出級晶體管NXP BLF6G20LS-140 140瓦射頻LDMOS。

輸出在Xinger II XC1900A-03S混合耦合器中重新組合,然后通過循環器進入雙工器。

多層板/特種板/難度板 極速打樣和小批量工廠

聚創立微信公眾號

聚創立微信公眾號

粵公網安備 44132202100173號

粵公網安備 44132202100173號